VHDL چیست؟

VHDL یک زبان برنامهنویسی است که برای توصیف مدارهای سختافزاری استفاده میشود. Vhdl مخفف چیست؟ این زبان از دو مخفف تشکیل شده است. اولین مخفف VHSIC به معنای Very High-Speed Integrated Circuit یعنی مدار مجتمع با سرعت بسیار بالا است. دومین مخفف زبان برنامه نویسی ویاچدیال نیز به معنای Hardware Description Language یا زبان توصیف سختافزار است (چقدر طولانی شد!).

هم رویش منتشر کرده است:

آموزش پایتون از صفر — برنامه نویسی مقدماتی تا پیشرفته Python

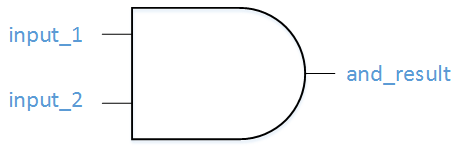

توصیف یک گیت AND با VHDL

بیایید با یک مثال ساده در VHDL شروع کنیم که یک گیت And را توصیف میکند. گیت And دو ورودی و یک خروجی دارد و خروجی فقط زمانی برابر ۱ است که هر دو ورودی برابر ۱ باشند. ما قصد داریم این گیت را با استفاده از VHDL توصیف کنیم.

در زبان برنامه نویسی ویاچدیال، واحدهای اصلی سیگنال نامیده میشوند. در این مثال، یک سیگنال میتواند دو وضعیت ۰ و ۱ را داشته باشد. حالا بیایید چند خط کد ساده VHDL را مشاهده کنیم:

signal and_gate : std_logic;

and_gate <= input_1 and input_2;

در کد بالا، یک سیگنال با نام “and_gate” تعریف میکنیم که از نوع “std_logic” است. این نوع بیشتر برای تعریف سیگنالها استفاده میشود. در این کد، یک گیت AND با یک خروجی به نام “and_gate” و دو ورودی به نامهای “input_1” و “input_2” ایجاد میشود. کلمه کلیدی “and” در VHDL رزرو شده است و نمیتوانیم از آن مثلاً بهعنوان اسم سیگنال استفاده کنیم. عملگر “<=” بهعنوان عملگر انتساب شناخته میشود. وقتی این قسمت کد را به صوت بلند میخوانید، میتوانید بگویید: “سیگنال “and_gate” دو ورودی ۱ و ورودی را AND میکند.”

entity در VHDL

اکنون شاید از خودتان بپرسید که ورودی-۱ و ورودی-۲ از کجا میآیند. خب، همانطور که از نامشان پیداست، آنها ورودیهای این گیت هستند، بنابراین باید ابتدا آنها را تعریف کنیم. در VHDL، تعریف ورودیها و خروجیها در یک قسمت به نام “entity” صورت میگیرد. entity شامل یک “پورت” است که تمام ورودیها و خروجیهای فایل را تعریف میکند. بیایید یک entity ساده ایجاد کنیم:

entity example_and is

port (

input_1 : in std_logic;

input_2 : in std_logic;

and_result : out std_logic

);

end example_and;

این قسمت، entity اصلی ماست. ما یک entity با نام “example_and” ایجاد کردیم که شامل ۳ سیگنال است، ۲ ورودی و ۱ خروجی، و همه آنها از نوع “std_logic” هستند. البته، در VHDL برخی نوعهای دیگری نیز وجود دارند که به آنها در آینده آشنا خواهید شد.

architecture در VHDL

یک کلمه کلیدی دیگر در VHDL به نام “architecture” یا “معماری” نیاز است تا entity را کامل کنیم. معماری برای توصیف عملکرد یک entity استفاده میشود. میتوانید آن را مانند یک مقاله پایاننامه تصور کنید: entity معادل فهرست مطالب و معماری محتوا را توصیف میکند. بیایید برای این entity یک معماری ایجاد کنیم.

architecture rtl of example_and is

signal and_gate : std_logic;

begin

and_gate <= input_1 and input_2;

and_result <= and_gate;

end rtl;

کد بالا یک معماری به نام “rtl” برای entity به نام “example_and” تعریف میکند. تمام سیگنالهایی که توسط این معماری استفاده میشوند باید بین کلمات کلیدی “is” و “begin” تعریف شوند. منطق واقعی معماری بین کلمه کلیدی “begin” و “end” قرار میگیرد.

کتابخانه در VHDL

کار با این فایل تقریباً تمام شده است. آخرین چیزی که باید تعریف کنید این است که از کدام کتابخانه استفاده شود. یک کتابخانه نحوه عملکرد برخی کلمات کلیدی را در فایل شما تعریف میکند. در حال حاضر، فقط بهعنوان یک فرض بپذیرید که باید این دو خط را در بالای فایل خود قرار دهید:

library ieee;

use ieee.std_logic_1164.all;

جمعبندی

تبریک میگویم! شما اولین فایل VHDL خود را ایجاد کردید. حالا میتوانید فایل کامل شده را اینجا مشاهده کنید.

library ieee;

use ieee.std_logic_1164.all;

entity example_and is

port (

input_1 : in std_logic;

input_2 : in std_logic;

and_result : out std_logic

);

end example_and;

architecture rtl of example_and is

signal and_gate : std_logic;

begin

and_gate <= input_1 and input_2;

and_result <= and_gate;

end rtl;

احتمالاً متوجه شدید که برای ایجاد یک گیت AND ساده، نیاز به نوشتن کد زیادی داشتید. درست است؛ VHDL یکزبان بسیار دقیق و جزئی است که برای توصیف سختافزارها استفاده میشود؛ بنابراین، انجام کارهایی که در نرمافزارها بسیار ساده هستند، در VHDL زمان بیشتری را میطلبد. اما با تمرین و تجربه، بهزودی با این زبان آشنا خواهید شد و بتوانید بهراحتی سختافزارهای پیچیدهتری را توصیف کنید.

کلیدواژگان

VHDL چیست | ویاچدیال چیست | آشنایی با زبان VHDL | آموزش VHDL به زبان ساده | زبان کدنویسی VHDL | زبان توصیف سخت افزار | Verilog |زبان برنامهنویسی ویاچدیال | VHDL | FPGA | ASIC | entity | توصیف مدارهای سختافزاری | Hardware Description Language | ویاچدیال | وریلاگ | مدارهای سختافزاری | Vhdl مخفف چیست | آشنایی با زبان vhdl | آشنایی با زبان وی اچ دی ال | معرفی زبان VHDL | آشنایی با زبان VHDL | زبان برنامه نویسی ویاچدیال

2 دیدگاه برای “VHDL چیست؟ — مقدمهای بر زبان برنامه نویسی توصیف مدارهای سختافزاری ”

یه مقاله بسیار خوندنی که با عشق نوشته شده! عالی بود.

خیلی ممنونم از لطف شما.